Time:2025-09-25 Browse: 1

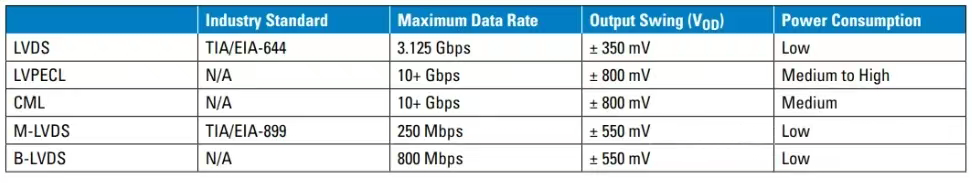

1. LVDS (Low Voltage Differential Signaling) is an electrical standard for signal transmission introduced in 1994 by National Semiconductor Corporation of the United States. It was largely developed to replace Emitter-Coupled Logic (ECL) or Positive Emitter-Coupled Logic (PECL). LVDS is a small-amplitude differential signaling technology that transmits data over a pair of differential PCB traces or balanced cables using very low-amplitude signals (approximately 350 mV). LVDS supports point-to-point or point-to-multipoint connections and features low power consumption, low bit error rate, low crosstalk, and low electromagnetic radiation. Its unique low-amplitude signaling and constant-current drive mode generate minimal noise and consume very little power, making it widely used in high-speed serial data communication applications such as backplanes, clock distribution, board-to-board data transmission, and cable-based data links.

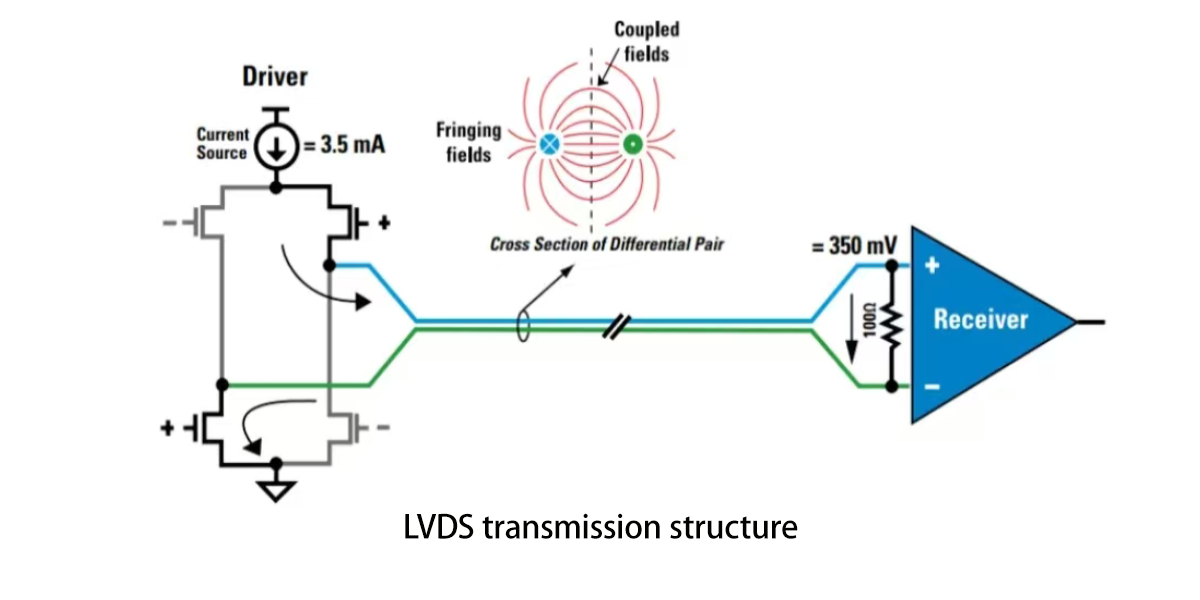

2. The LVDS transmission architecture follows the TIA/EIA-644 standard and is designed specifically for the physical layer, meaning it focuses on signal transmission at the electrical level without involving data transmission protocols. An LVDS signal transmission system typically consists of three main components: a differential transmitter, a differential receiver, and a differential interconnect.

● Differential Transmitter: Converts single-ended TTL signals into balanced LVDS signals for differential transmission.

● Differential Receiver: Converts received balanced LVDS signals back into single-ended TTL signals.

● Differential Interconnect: Includes connecting media (such as cables or PCB traces) and a termination resistor. According to IEEE specifications, the termination resistor is typically 100 Ω.

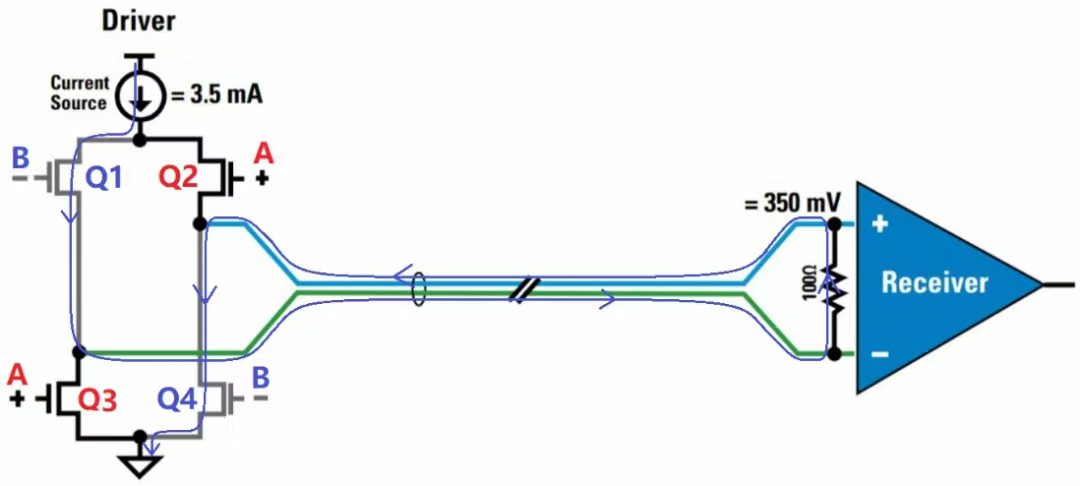

3. LVDS Operating Principle: The LVDS driver consists of a constant current source that drives the differential line, typically set at 3.5 mA. The LVDS receiver has very high input impedance (drawing almost no current), so most of the current from the driver flows through the 100 Ω termination resistor, generating a voltage of approximately 350 mV across the receiver's input terminals. When the driver switches state, the direction of the current through the resistor reverses, producing the corresponding logic "1" and logic "0" states.

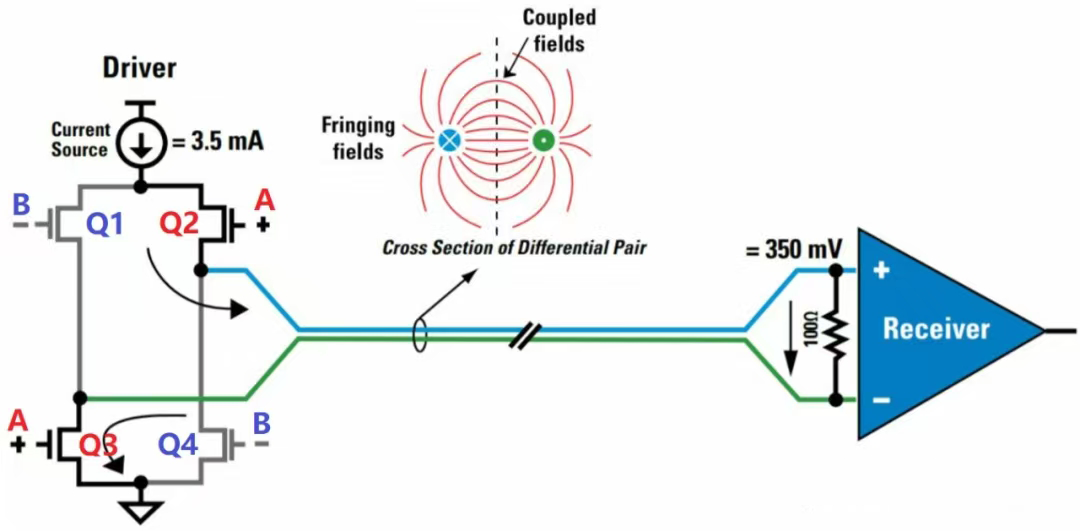

Output Logic "1": The LVDS output stage employs a 3.5 mA current source and consists of two pairs of MOSFETs (four transistors) forming a differential output pair. When A+ is turned on and B- is turned off, the current from the constant current source flows through Q2 (the A+ MOSFET), drives the output, passes through the 100 Ω termination resistor, returns via Q3 (the A+ MOSFET) to the driver side, and is connected to GND. This current path generates an output voltage across the 100 Ω termination resistor of: 3.5 mA × 100 Ω = 350 mV, representing logic "1". The direction of the current is as shown in the figure below:

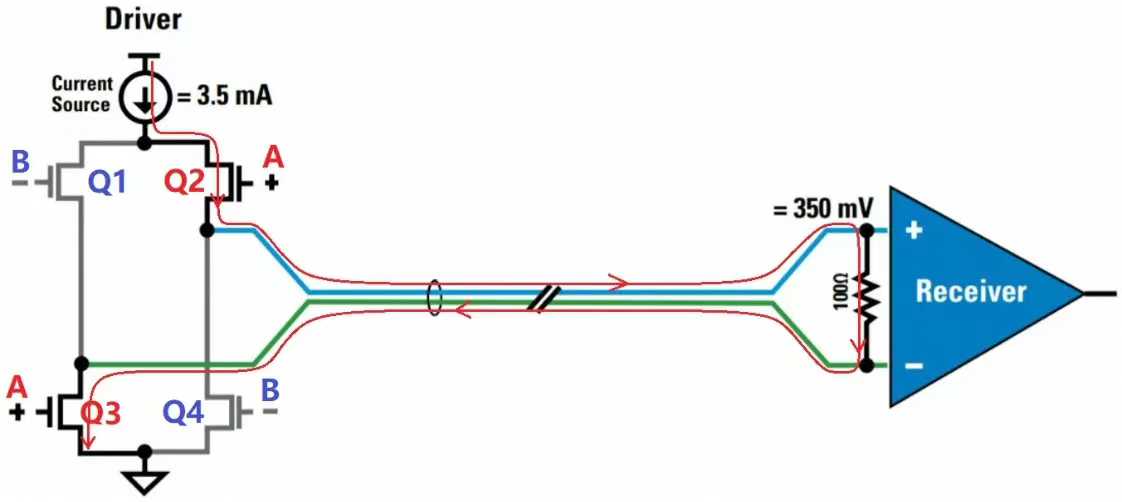

Output Logic "0": When B− is turned on and A+ is turned off, the 3.5 mA drive current flows out from Q1 (the B− MOSFET), passes through the 100 Ω termination resistor, returns via Q4 (the B− MOSFET) in the driver to GND. This current path also generates a voltage across the 100 Ω termination resistor, but the current direction is opposite to that of the "A+ on, B− off" state. As a result, a reverse voltage is produced: −3.5 mA × 100 Ω = −350 mV, representing logic "0". The current direction is as shown in the figure below:

4. LVDS Characteristics:

① Differential Transmission: LVDS signals use a differential transmission method, meaning each signal line has a corresponding complementary (inverted) signal line. The voltage difference between the signal line and its complementary line is symmetric in positive and negative levels. This differential approach helps reduce interference and suppress crosstalk, thereby improving signal quality and stability.

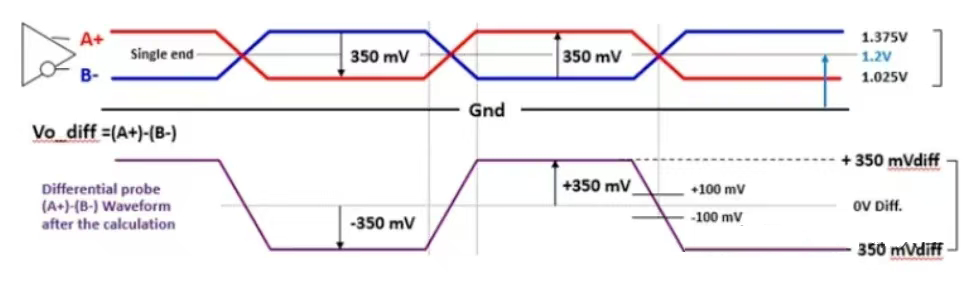

② Voltage Characteristics: The two LVDS differential signal lines—positive (A+) and negative (B−)—have a common-mode bias voltage of 1.2 V and a differential voltage swing of 350 mV. If we measure the signal waveforms using an oscilloscope and compute the difference between the two voltages: (A+) − (B−), the resulting differential swing will be −350 mV for logic "0" and +350 mV for logic "1". The waveform is shown in the figure below:

③ Constant-Current Drive: LVDS employs a 3.5 mA constant-current source driving architecture. The signal forms a loop through a 100 Ω termination resistor, and the differential voltage is generated across this resistor as the current flows through it. This design ensures a stable output signal amplitude that is insensitive to minor load variations, while also avoiding issues such as overshoot and undershoot commonly seen in traditional voltage-driven systems.

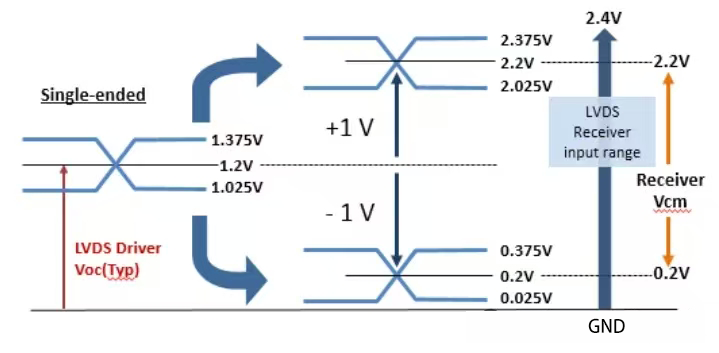

④ Common-Mode Voltage Range: LVDS receivers have a wide input common-mode voltage range, typically from 0.2 V to 2.2 V. They can tolerate a ground potential difference (commonly referred to as "ground bounce") of up to ±1 V between the transmitter and receiver. This means that while the transmitter typically outputs signals with a 1.2 V common-mode voltage, the receiver can accurately detect signals within this wide voltage range.

④ Common-Mode Voltage Range: LVDS receivers have a wide input common-mode voltage range, typically from 0.2 V to 2.2 V. They can tolerate a ground potential difference (commonly referred to as "ground bounce") of up to ±1 V between the transmitter and receiver. This means that while the transmitter typically outputs signals with a 1.2 V common-mode voltage, the receiver can accurately detect signals within this wide voltage range.

⑤ Termination Resistor: The standard mandates a 100 Ω ±10% termination resistor to be connected in parallel at the "receiver end" of the LVDS signal (typically a high-precision surface-mount resistor), and the resistor should be placed as close as possible to the receiver pins. The purpose is to "absorb" the signal energy at the end of the transmission line and prevent signal reflections.

⑥ Data Rate: LVDS supports high-speed data transmission, with typical rates ranging from 155 Mbps to 3.125 Gbps, and even higher in some applications.

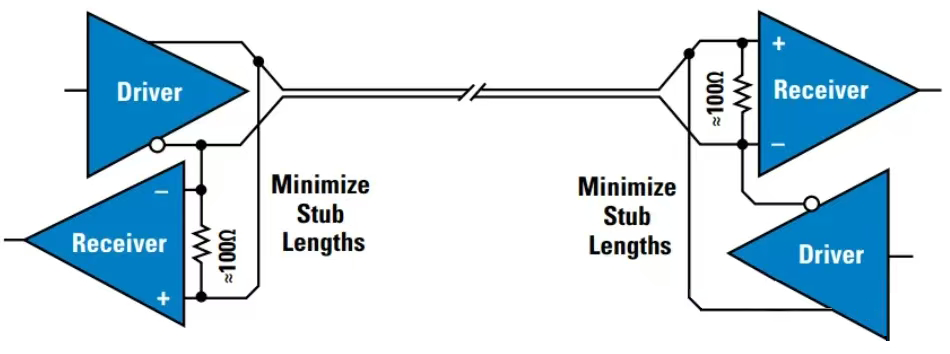

⑦ Half-Duplex Communication: From the perspective of LVDS transmission structure, a single pair of differential signal lines can only transmit data in one direction, meaning LVDS is inherently a simplex communication interface. However, common interfaces such as USB also use only one pair of differential lines but are capable of bidirectional communication. This is because LVDS systems often employ two sets of transmitters and receivers combined together, as shown in the figure. Therefore, LVDS is essentially a half-duplex communication technology.

⑧ Physical Interface: LVDS signals are transmitted using two balanced twisted-pair wires, with one pair carrying the positive signal and the other pair carrying the complementary (negative) signal.

⑨ Transmission Distance: LVDS signals can achieve transmission distances of over 15 meters. This is primarily due to the differential transmission method, which effectively cancels out electromagnetic interference between the signal lines and suppresses crosstalk.

⑩ Multi-Channel Expansion: LVDS can easily scale bandwidth through a "multiple parallel differential pairs" design (e.g., 4 pairs, 8 pairs). For example, 8 differential pairs can achieve a total data rate exceeding 12 Gbps, making it suitable for high-resolution video data transmission applications.

⑪ Low Power Consumption: The power consumption of LVDS remains nearly constant regardless of the data rate, because the signal swing is fixed (350 mV) and the drive current is constant (3.5 mA). Whether the data rate is 100 Mbps or 1 Gbps, the dynamic power consumption per differential pair remains stable at approximately 1.225 mW.

5. LVDS Applications

① Display Interfaces: LVDS is a standard interface for computers, LCD monitors, televisions, and other display devices, capable of providing high-speed and high-quality video signal transmission.

② Audio Signal Transmission: LVDS supports high-speed transmission of both audio and video signals, making it widely used in applications such as home theater systems, digital audio equipment, and cameras.

③ Industrial Automation: LVDS can be used for high-speed data transmission and control signal transmission in industrial automation systems.

④ Automotive Electronics: LVDS is applicable in the automotive electronics field—for example, controlling the brightness and contrast of displays on car seats, as well as being used in in-vehicle audio and video systems.

6. LVDS Termination Methods: In practical applications, LVDS employs different termination methods depending on factors such as common-mode voltage and signal swing, and sometimes must be adapted for different logic standards. Below are the commonly used LVDS configurations and termination methods.

① DC Coupling

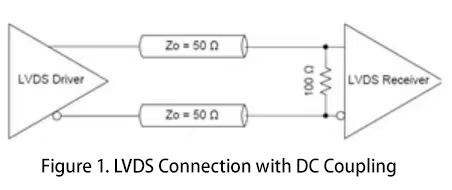

● DC coupling involves placing a 100 Ω differential termination resistor across the differential signal lines at the receiver end. This termination resistor should be placed as close as possible to the receiver to generate the differential voltage at the input and to match the characteristic impedance of the transmission line, thereby minimizing signal reflections.

● DC coupling involves placing a 100 Ω differential termination resistor across the differential signal lines at the receiver end. This termination resistor should be placed as close as possible to the receiver to generate the differential voltage at the input and to match the characteristic impedance of the transmission line, thereby minimizing signal reflections.

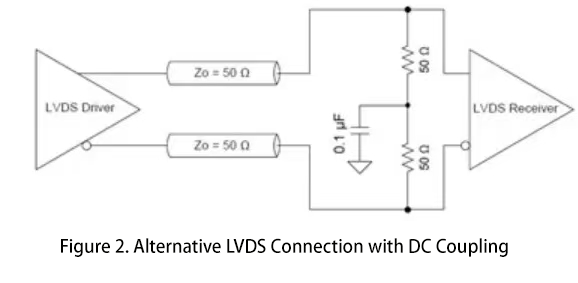

● Another termination method uses two 50 Ω resistors for split termination, with a capacitor connected to ground at the midpoint. This capacitor helps filter out common-mode noise and suppresses DC offset that may arise from mismatches in the differential traces or imbalances in the driver output. The value of the capacitor depends on the operating frequency; a 0.1 µF capacitor is generally sufficient for most high-speed data rates (1 Mbps and above).

● Another termination method uses two 50 Ω resistors for split termination, with a capacitor connected to ground at the midpoint. This capacitor helps filter out common-mode noise and suppresses DC offset that may arise from mismatches in the differential traces or imbalances in the driver output. The value of the capacitor depends on the operating frequency; a 0.1 µF capacitor is generally sufficient for most high-speed data rates (1 Mbps and above).

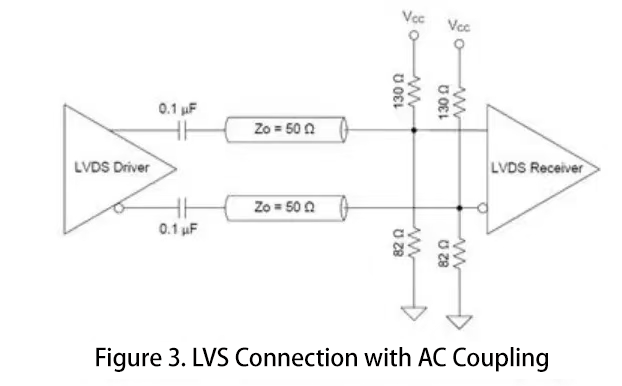

② AC Coupling: The resistor network at the receiver input restores the DC common-mode voltage to 1.2 V (assuming Vcc = 3.3 V), which is the midpoint of the standard LVDS receiver's input common-mode voltage range. Additionally, the resistor network provides a 100 Ω termination at the receiver's input. If termination resistors are already integrated within the LVDS receiver, larger external resistor values should be selected to avoid altering the effective termination impedance at the receiver input. A recommended pull-up resistor value is 10 kΩ and a pull-down resistor value is 5.7 kΩ. The value of the AC coupling capacitor depends on the operating frequency, as it blocks the DC component; a 0.1 µF capacitor is generally sufficient for high data rates (1 Mbps and above).

② AC Coupling: The resistor network at the receiver input restores the DC common-mode voltage to 1.2 V (assuming Vcc = 3.3 V), which is the midpoint of the standard LVDS receiver's input common-mode voltage range. Additionally, the resistor network provides a 100 Ω termination at the receiver's input. If termination resistors are already integrated within the LVDS receiver, larger external resistor values should be selected to avoid altering the effective termination impedance at the receiver input. A recommended pull-up resistor value is 10 kΩ and a pull-down resistor value is 5.7 kΩ. The value of the AC coupling capacitor depends on the operating frequency, as it blocks the DC component; a 0.1 µF capacitor is generally sufficient for high data rates (1 Mbps and above).

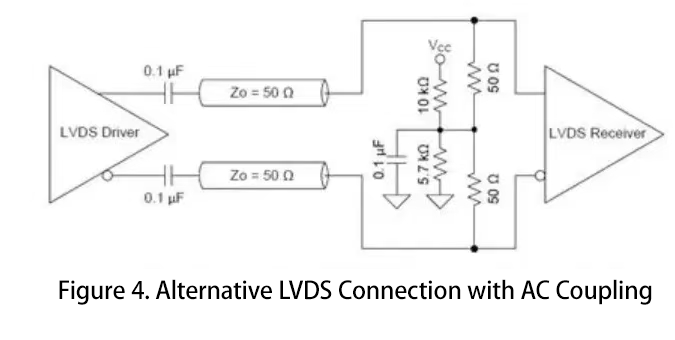

The left figure shows another circuit configuration that, in addition to the bias resistor network, employs split termination with a capacitor connected to ground at the midpoint. This capacitor helps filter out common-mode noise and reduces transmission line offset. Compared to the circuit described above, this configuration has the advantage of lower power consumption.

The left figure shows another circuit configuration that, in addition to the bias resistor network, employs split termination with a capacitor connected to ground at the midpoint. This capacitor helps filter out common-mode noise and reduces transmission line offset. Compared to the circuit described above, this configuration has the advantage of lower power consumption.